Barramento I2C — atribuição, dispositivo, transferência de dados, endereçamento

Ao criar um circuito eletrônico, muitos desenvolvedores se deparam com a necessidade de usar um grande número de chips intermediários para combinar, amostrar e endereçar seus blocos individuais. Para minimizar o número de chips auxiliares, a Philips propôs uma interface de rede serial I2C bidirecional de dois fios na década de 1980, projetada especificamente para gerenciar vários chips em um único dispositivo.

Hoje, a Philips sozinha produz mais de cem dispositivos compatíveis com I2C para equipamentos eletrônicos com uma ampla variedade de finalidades: memória, sistemas de processamento de vídeo, conversores analógico-digital e digital-analógico, drivers de vídeo, etc.

O barramento I2C é uma modificação do protocolo de troca de dados serial capaz de transmitir dados seriais de 8 bits no modo "rápido" usual a taxas de 100 a 400 kbps. O processo de troca de dados é implementado aqui em apenas dois fios (sem contar o fio comum): linha SDA para dados e linha SCL para sincronização.

O barramento torna-se bidirecional devido ao fato das cascatas de saídas dos dispositivos conectados ao barramento possuírem coletores ou canais abertos, replicando assim a fiação do AND. Como resultado, o barramento minimiza o número de conexões entre os chips, deixando menos pinos e traços necessários na placa. Como resultado, a própria placa acaba sendo mais simples, compacta e tecnologicamente mais avançada na produção.

Este protocolo permite desabilitar decodificadores de endereço e outras lógicas de negociação externa. O número de chips que podem operar simultaneamente no barramento I2C é limitado por sua capacidade — no máximo 400 pF.

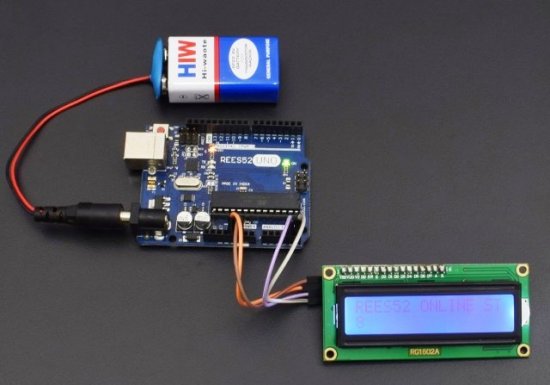

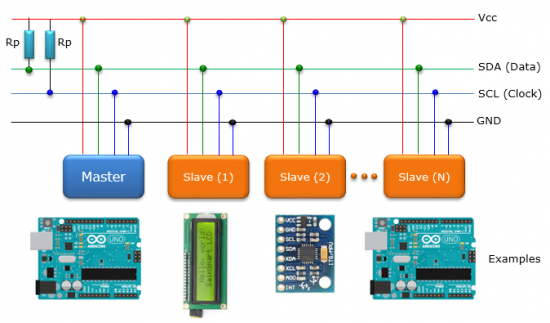

Os ICs compatíveis com I2C possuem um algoritmo de supressão de ruído de hardware para garantir a integridade dos dados mesmo na presença de forte interferência. Tais dispositivos possuem uma interface que permite que os microcircuitos se comuniquem mesmo quando suas tensões de alimentação são diferentes. Na figura abaixo, você pode se familiarizar com o princípio de conectar vários microcircuitos por meio de um barramento comum.

Cada um dos dispositivos conectados ao barramento tem seu próprio endereço único, é determinado por ele e, de acordo com a finalidade do dispositivo, pode funcionar como receptor ou como transmissor. Ao transmitir dados, esses dispositivos podem ser master (master) ou slave (slave). O mestre é o dispositivo que inicia a transferência de dados e gera sinais de clock na linha SCL. O escravo, em relação ao mestre, é o dispositivo de destino.

A qualquer momento da operação no barramento I2C, apenas um dispositivo pode atuar como mestre; ele gera um sinal na linha SCL.Um mestre pode ser um receptor mestre ou um transmissor mestre.

Em princípio, o barramento permite vários mestres diferentes, mas impõe restrições nas características de formação de sinais de controle e monitoramento do estado do barramento; isso significa que vários mestres podem começar a transmitir ao mesmo tempo, mas conflitos desse tipo são eliminados graças à arbitragem, ou seja, a forma como o mestre se comporta quando detecta que o barramento está ocupado por outro mestre.

A sincronização de um par de dispositivos é garantida pelo fato de todos os dispositivos estarem conectados ao barramento, formando uma fiação "AND". Inicialmente, os sinais SDA e SCL são altos.

INICIAR e PARAR

A troca começa com o mestre gerando o estado «START»: na linha SDA, o sinal vai do estado alto para o baixo, enquanto a linha SCL tem um nível alto estável. Todos os dispositivos conectados ao barramento percebem esta situação como um comando para iniciar a troca.

Cada mestre gera um sinal de clock individual na linha SCL ao transmitir dados no barramento.

A troca termina com a formação do estado STOP pelo mestre: na linha SDA o sinal muda de baixo para alto, enquanto a linha SCL tem um nível alto estável.

O motorista sempre atua como a fonte dos sinais START e STOP. Assim que o sinal «START» for fixado, significa que a linha está ocupada. A linha está livre quando um sinal STOP é detectado.

Imediatamente após declarar o estado START, o mestre muda a linha SCL para baixo e envia o bit mais significativo do primeiro byte de mensagem para a linha SDA. O número de bytes em uma mensagem não é limitado.Alterações na linha SDA são habilitadas apenas quando o nível do sinal na linha SCL é baixo. Os dados são válidos e não devem ser alterados apenas quando o pulso de sincronismo estiver alto.

A confirmação de que o byte do transmissor mestre foi recebido pelo receptor escravo é feita configurando um bit de confirmação especial na linha SDA após o oitavo bit de dados ter sido recebido.

A CONFIRMAÇÃO

Assim, enviar 8 bits de dados do transmissor para o receptor acaba com um pulso extra na linha SCL quando o dispositivo receptor fica baixo na linha SDA, indicando que recebeu o byte inteiro.

A confirmação é parte integrante do processo de transferência de dados. O mestre gera um pulso de sincronização. O transmissor envia um estado baixo para SDA enquanto o relógio de reconhecimento está ativo. Enquanto o pulso de sincronismo estiver alto, o receptor deve manter o SDA baixo.

Se o escravo de destino não confirmar seu endereço, por exemplo, porque está ocupado no momento, a linha de dados deve ser mantida alta. O mestre pode então dar um sinal STOP para abortar o despacho.

Se a recepção for realizada pelo receptor mestre, ele é obrigado a informar o transmissor escravo após a conclusão da transmissão - não confirmando o último byte. O transmissor escravo libera a linha de dados para que o mestre possa emitir um sinal STOP ou um sinal START repetitivo.

A sincronização dos dispositivos é garantida pelo fato de que as conexões à linha SCL são feitas de acordo com o princípio "AND".

O mestre não tem o direito exclusivo de controlar a transição da linha SCL de baixo para alto.Se o escravo precisar de mais tempo para processar um bit recebido, ele pode manter SCL baixo de forma independente até que esteja pronto para receber o próximo bit de dados. A linha SCL em tal situação será baixa durante o pulso de sincronismo de baixo nível mais longo.

Os dispositivos com a baixa sustentada mais baixa permanecerão ociosos até que o longo período termine. Quando todos os dispositivos terminarem o período de baixa sincronização, o SCL ficará alto.

Todos os dispositivos começarão com clock alto e o primeiro dispositivo a completar seu período será o primeiro a definir a linha SCL baixa. Como resultado, a duração do estado baixo do SCL será determinada pelo mais longo estado baixo do pulso de sincronização de um dos dispositivos, e a duração do estado alto será determinada pelo menor período de sincronização de um dos dispositivos.

Os sinais de sincronização podem ser usados pelos receptores como um meio de controlar a transmissão de dados no nível de bit e byte.

Se o dispositivo é capaz de receber bytes em alta taxa, mas leva um certo tempo para armazenar o byte recebido ou se preparar para receber o próximo byte, ele pode continuar mantendo o SCL baixo após receber e reconhecer um byte, forçando o transmissor em um estado de espera.

Um microcontrolador sem circuitos de hardware embutidos, por exemplo, no nível de bit, pode diminuir a velocidade do clock aumentando a duração de seu estado baixo. Como resultado, a taxa de transmissão do dispositivo mestre será determinada pela velocidade do dispositivo mais lento.

ENDEREÇO

Cada dispositivo conectado ao barramento I2C possui um endereço de programa exclusivo no qual o mestre o endereça enviando um comando específico. Os microcircuitos do mesmo tipo são caracterizados por um seletor de endereço, implementado na forma de entradas digitais do seletor ou na forma analógica. Os endereços são divididos no espaço de endereços dos dispositivos conectados ao barramento.

O modo normal assume o endereçamento de sete bits. O endereçamento funciona da seguinte forma: após o comando «START», o mestre envia o primeiro byte, que determina qual dispositivo escravo é necessário para se comunicar com o mestre. Existe também um endereço de chamada comum que define todos os dispositivos no barramento, todos os dispositivos (teoricamente) respondem a ele com uma confirmação, mas na prática isso é raro.

Portanto, os primeiros sete bits do primeiro byte são o endereço do escravo. O bit menos significativo, o oitavo, indica a direção do envio dos dados. Se houver um «0», então a informação será escrita do mestre para este escravo. Se «1», a informação será lida pelo mestre a partir deste escravo.

Depois que o mestre termina de enviar o byte de endereço, cada escravo compara seu endereço com ele. Qualquer pessoa com o mesmo endereço é um escravo e é definido como transmissor ou receptor escravo, dependendo do valor do bit menos significativo do byte de endereço.

Um endereço escravo pode incluir partes fixas e programáveis. Muitas vezes, um grande número de dispositivos do mesmo tipo funciona em um sistema, então a parte programável do endereço permite o uso de no máximo dispositivos do mesmo tipo no barramento. Quantos bits no byte de endereço são programáveis depende do número de pinos livres no chip.

Às vezes, um pino com uma configuração analógica da faixa de endereço programável é suficiente, por exemplo, o SAA1064 - um driver de indicador de LED que possui exatamente essa implementação. O potencial de um determinado pino determina o deslocamento do espaço de endereço do chip para que chips do mesmo tipo não entrem em conflito operando no mesmo barramento. Todos os chips que suportam o barramento I2C contêm um conjunto de endereços que o fabricante especifica na documentação.

A combinação «11110XX» é reservada para endereçamento de 10 bits. Se imaginarmos a troca de dados do comando «START» para o comando «STOP», ficará assim:

Formatos de troca de dados simples e combinados são permitidos aqui. O formato combinado significa que entre «START» e «STOP» o mestre e o escravo podem atuar como receptores e transmissores, o que é útil, por exemplo, no gerenciamento de memória serial.

Deixe o primeiro byte de dados transferir um endereço de memória. Então, repetindo o comando «START» e lendo o endereço do escravo, os dados da memória funcionarão. As decisões de incrementar ou decrementar automaticamente o endereço acessado anteriormente são tomadas pelo desenvolvedor do dispositivo após ter estudado previamente a documentação do chip. De uma forma ou de outra, após receber o comando START, todos os dispositivos devem restaurar sua lógica e se preparar para o fato de que o endereço agora será nomeado.